本篇目录:

Modelsim软件如何仿真,怎么能添加输入信号

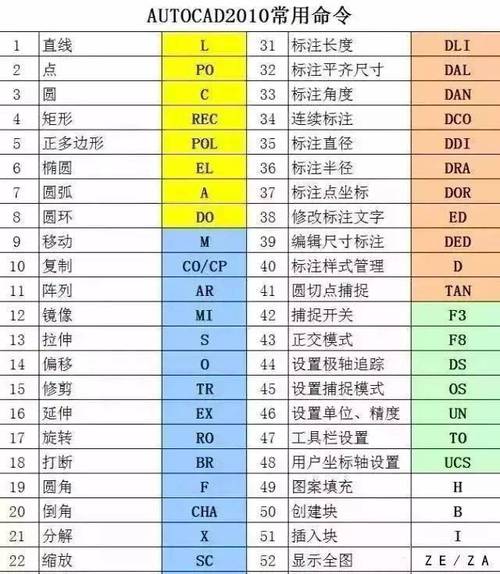

1、asyn_fifo.v 是该核的行为模型,主要调用了 xilinx 行为模型库的模块,仿真时该文件也要加入工程。调试方便。

2、step5:打开signal窗口(view-signal)和wave窗口(view-signal),将你希望仿真的信号添加进去。Step:仿真。。利用ModelSim SE0C实现时序仿真!!1) 打开一个工程文件。

3、做好仿真(仿真波形之前保存了,如果正在仿真,那更好),那么打开波形文件。找到tools-editpreferences。找到bywindows-wavewindows,可以看到一系列可以更改颜色的列表。

modelsim仿真

1、首先断网可以解决一直卡在loading的问题,断开网络连接再重新连接,显示loading后会成功显示。找到你的电脑modelsim安装目录搜索modelsim.ini打开,定位到VoptFlow,将其值设为0,即关闭设计的自动优化。

2、下面图中红色框中的部分就是被注释掉的库编译部分,这样会节省我们的仿真时间,注意在脚本语言中#是注释符。

3、这个问题可能是由于在使用ModelSim进行仿真时,未正确安装或配置所导致的。以下是一些常见的解决方法:确认你的ModelSim版本是否与你的操作系统兼容。如果你的操作系统是64位的,那么你应该使用64位的ModelSim版本。

如何对多个文件进行MODELSIM仿真?

pll,ram,都要把.v文件加入modelsim,或者在主程序里面include并例化。另外altsyncram貌似是从altera的FPGA中生成的,所以必须加入tb_altera_mf.v文件才行。

step5:打开signal窗口(view-signal)和wave窗口(view-signal),将你希望仿真的信号添加进去。Step:仿真。。利用ModelSim SE0C实现时序仿真!!1) 打开一个工程文件。

但是这里的Functional是基于门级网表的功能仿真,并不是HDL级的功能仿真。首先需要将.bdf原理图文件转换为Verilog HDL等第三方EDA工具所支持的标准描述文件。

完成库的编译之后,就是添加库到ModelSim的仿真环境中,修改modelsim安装目录下的modelsim.ini,这样就完成了库的添加,在仿真时,仅需要填加生成ip的.v文件。

网上的很多教程都是把这些文件一起编译,这样适用于Verilog和VHDL混合仿真,但如果只用一种语言,如Verilog则完全没必要全部编译。下面以该目录下的altera_mf.v为例介绍建立预编译库的方法。

到此,以上就是小编对于的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏